全球内存产业已进入一个必须寻求新兴替代技术的时代。在多样化的次世代内存技术中,为何电阻式内存,在类神经仿生运算的应用上值得期待?其更被业界认为是最有机会成为下世代通用内存的选择,同时也是目前投入研发厂商最多之技术?

迈入寻求全新嵌入式非挥发性内存技术的时代

近年来由于物联网、行动装置、高速计算机和智能汽车等产业的快速发展,大幅推升了人工智能(AI)及边缘计算(Edge Computing)等巨量运算架构的应用需求,也因此既有高容量存储组件例如 DRAM 及 NAND Flash,其在耗电量及数据访问速度上已无法跟上需求的脚步。

并且,随着半导体制程线宽缩微已超越 14nm、晶体管发展主流迁移到 FinFET 或 GAA 等先进结构,长期应用于 CMOS 芯片上存储的嵌入式 NOR Flash 碍于「闪存缩放限制(Flash Memory Scaling Limit)」问题,也已无法跟上 SoC 芯片整合制程的发展要求,必须要有全新的嵌入式非挥发性内存技术,才能搭配下一世代以先进制程所制造的 ASIC 和 MCU。

电阻式内存为何备受期待?

过去数十年来在世界各国合力开发下,已初略成形的次世代非挥发性内存技术包括铁电内存(FRAM)、相变化内存(PRAM)、磁阻式内存(MRAM)、以及电阻式内存(RRAM)等。这些候选的新兴技术,不仅读写速度都比 NAND Flash 要快 1,000 倍以上,并且皆能够在奈安培(nA)的极低电流下操作。同时,也都具有潜力可突破范纽曼(von Neumann)架构瓶颈,实现内存内运算(In-memory Computing)之能力。

在多样化的次世代内存技术中,电阻式内存由于相对具有读写快速、低耗能、结构简单、数据储存时间长、重复操作可靠度佳与成本便宜等产品优势,以及适合应用于类神经仿生运算的电导(电阻)渐变模拟特性,被业界认为是最有机会成为下世代通用内存的选择,同时也是目前投入研发厂商最多之技术,包含 Adesto(2020 年已被 Dialog 并购)、Crossbar、Samsung、Panasonic、Micron、Hynix 及 Intel 等公司,都各别拥有不同的电阻式内存技术。

电阻式内存由来

电阻式内存(Resistive Random Access Memory, RRAM)结构为简单的金属-绝缘层-金属(Metal-Insulator-Metal, MIM),其原理为施予电压或电流操作,利用物质电阻改变组件的高低电阻状态,达成数字讯号储存效果。

电阻式内存最早起源自 1960 年代,研究学者 Hickmott 发现氧化铝(AlOx)材料经过电压或电流操作后,其电阻状态会因此改变 [1];近年来,研究发现氧化镍(NiO)[2-5]、氧化钛(TiOx)[6-9]、氧化铪(HfOx)[10-13] 等绝缘体材料,亦可用于 RRAM 的中间绝缘层。RRAM 可利用特定的电压来读取不同状态的电阻值(电流值),进而判读组件「1」和「0」的逻辑状态。此外,RRAM 具有良好的非挥发性记忆特性,其讯号储存状态可在不施加外在偏压的情况下,保存至下一次讯号的写入或抹除。

RRAM 物理机制与操作特性

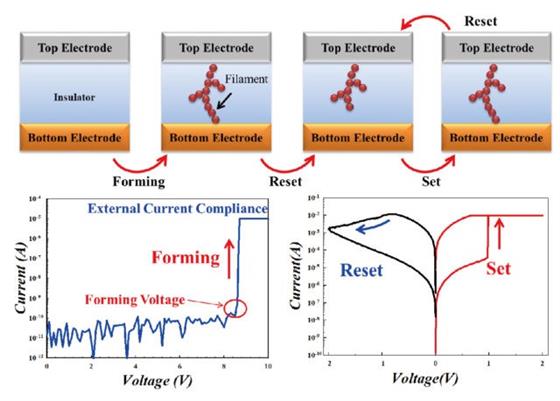

RRAM 的物理机制目前较受到注目的是灯丝理论(Filament Theory)[14-16],普遍认为 RRAM 的操作方式是在一开始时给予组件一较大的外加偏压,使氧化物绝缘层内部形成导通路径,此时绝缘层会变为低阻态(Low Resistance State, LRS),此过程通常需要限制电流(Compliance Current),避免电流过大反应剧烈使组件永久崩溃,此步骤称之为 Forming。

接着以组件偏压控制氧离子与氧空缺复合,使导通路径阻断,进而从低电阻态(LRS)回到高电阻态(High Resistance State, HRS),此过程称为 Reset;而再次给予小于 Forming 所需的电压,即可将阻断的导通路径重新连接,从高阻态(HRS)再次回到低阻态(LRS),此步骤称为 Set。

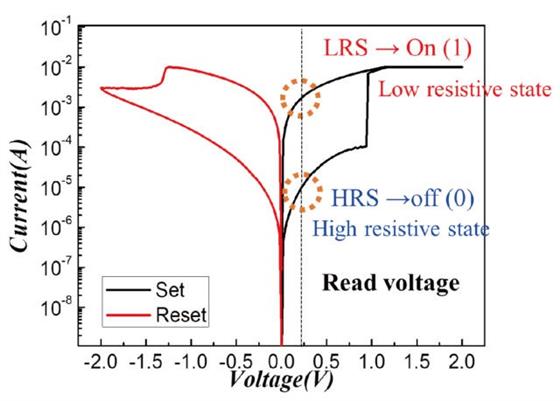

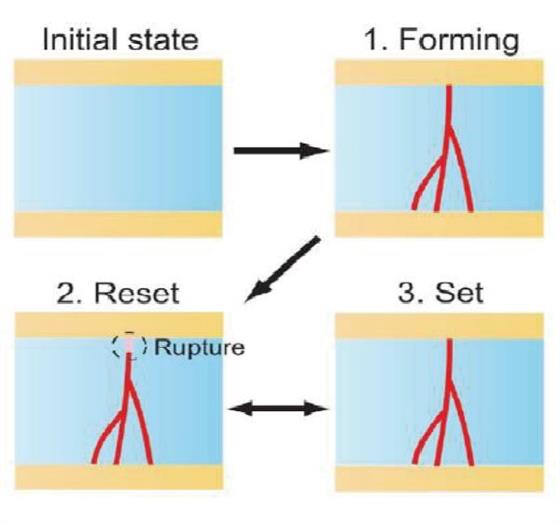

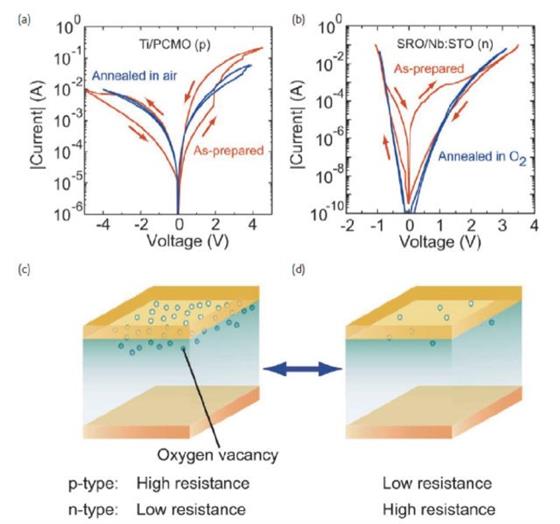

来回操作 Set 与 Reset process 就可以达成 RRAM 的写入与抹除,RRAM 的操作流程如图 1 所示,而在读取方面主要是藉由一微小的读取电压来判读不同的电阻值,以分辨数字讯号 0 和 1(图 2)。RRAM 依阻值状态变化的不同可区分为阻丝型与界面型,阻丝型 RRAM 即于上下两电极间有一连续传导路径(图 3),也是目前 RRAM 在传导机制中较受到广泛认同的类型;另一为接口型 RRAM(图4),透过施加外部电压,使绝缘体层中形成氧空缺或载子电荷进行电子传递使其阻态改变,当氧空缺或载子电荷变多,其电流增大,因此组件电极间的绝缘体层面积大小会影响阻态变化。

▲图 1 RRAM 切换流程与电性输出图

▲图 2 RRAM 用于数字内存判读方式

▲图 3 灯丝型 RRAM 操作过程 [14]

▲图 4 接口型 RRAM 输出特性曲线与操作原理 [14]

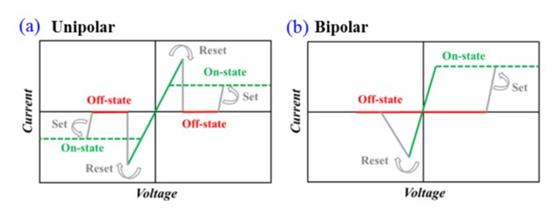

RRAM 操作方式分为两种特性:

- 单极性(Unipolar):如图 5(a)所示,此种可藉由单一方向的电压即可作 Set 与 Reset 操作,Reset 过程以焦耳热(Joule Heating)造成电阻灯丝熔断使得阻态变化。

- 双极性(Bipolar):指的操作电压需相反才能进行 Set 与 Reset,而阻态能切换的原因则主要认为来自于氧离子移动,对电阻灯丝进行氧化还原作用,使其有高低阻态变化,如图 5(b)所示。

▲图 5 RRAM 操作方式(a)单极性操作(Unipolar)、(b)双极性操作(Bipolar)[17]

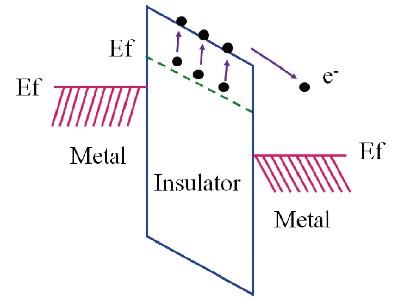

理想的金属/绝缘体/金属结构中,中间的绝缘层在施加偏压时并不会有电流通过,但实际上当组件受到过大电场或温度时,载子能在绝缘层中移动传导,而有漏电流的产生,进而读出 HRS。其中电流的移动机制可利用电流-电压进行电流机制拟合(Current-Fitting)评估在绝缘层间电流主要透过何种机制进行移动,其传输机制主要可分为以下几种:

- 奥姆传导机制(Ohmic Conduction):

主要以位于导电带(Conduction Band)的自由电子(Free Electron)与价电带(Valence Band)的电洞当作载子传输的机制,在一小电压下电阻为常数,与电流呈线性关系。图 6 为 RRAM 结构的奥姆传导能带示意图,材料中的载子受到外加电场的作用移动,进而产生电流 [18]。

▲图 6 奥姆传导之能带图

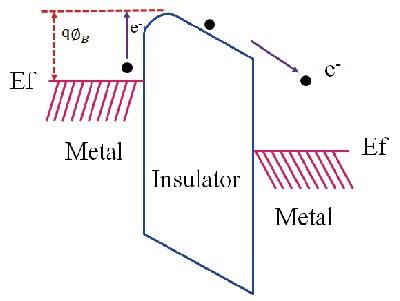

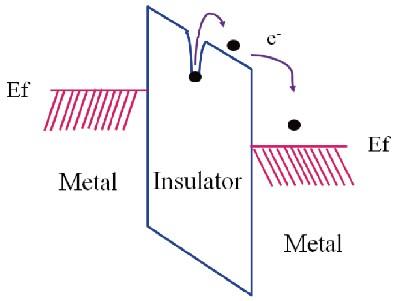

- 萧基发射(Schottky Emission):

一般金属与绝缘体的接面会存在着能障高度(Barrier Height),此能障高度指的是绝缘体电子亲和力与金属功函数之间差值。图 7 所示为一RRAM 之能带图,施加外加电场情形下与电子通过金属表面时产生的镜像电荷,使能障高度下降,电子透过热激发影响越过能障高度,电子能在绝缘体的传导带上传递,而产生电流称为萧基发射(Schottky Emission)[19]。

▲图 7 萧基发射之能带图

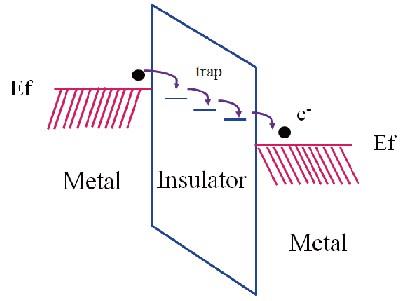

- 法兰克–普尔发射(Frenkel- Poole Emission):

此传导机制与萧基发射类似,同样受到外加电场影响,电子因热激发获得能量,且载子跳至价电带或导电带的能障高度降低,使载子能越过能障高度跳至价电带或导电带,进而由导带传递产生电流。此时的能障高度指的是在沉积绝缘体或半导体薄膜时,薄膜所产生的悬浮键或是缺陷,这些缺陷会在靠近价电带或导电带的边缘形成缺陷能阶,而缺陷能阶到价电带或导电带之间的差值,即为法兰克-普尔发射(Frenkel-Poole Emission)所需越过之能障高度 [20],如图 8 所示其能带图。

▲图 8 法兰克-普尔发射之能带图

- 跳跃传导(Hopping Conduction):

若薄膜之中含有许多连续缺陷存在时,这些连续缺陷会在绝缘体中产生连续缺陷能阶,此时不需将电子激发至导电带,而是藉由彼此相近的缺陷能阶进行跳跃传递,进而产生电流。当缺陷彼此间距离越小时,其电子跳越能阶所需之活化能越小,称为跳跃传导(Hopping Conduction),其能带图如图 9 所示 [21]。

▲图 9 跳跃传导之能带图

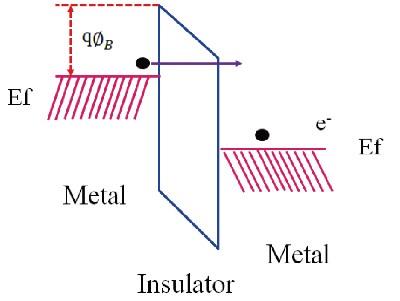

- 穿隧传导(Tunneling):

主要是当外加电场过大时,能带图 Ec、Ev 更倾斜(两侧电压差更大),使得绝缘体能带变薄,电子可直接穿隧过绝缘层至另一侧产生电流,其能带图如图 10 所示 [22]。

▲图 10 穿隧传导之能带图

- 空间限制电流传导(Space Charge Limited Current):

当绝缘体单边或双边形成奥姆接触时,电极能不间断地提供载子,当接触电极将电子注入至绝缘体或半导体的传导带时,由于载子注入速率大于复合速率,电荷会在绝缘体内慢慢累积,进而影响电流流动,此为空间限制电流传导(Space Charge Limited Current),能带图如图 11 所示 [23]。

▲图 11 空间限制电流之能带图

提高密度的交叉数组结构,以及解决潜行电流的 1T1R 架构

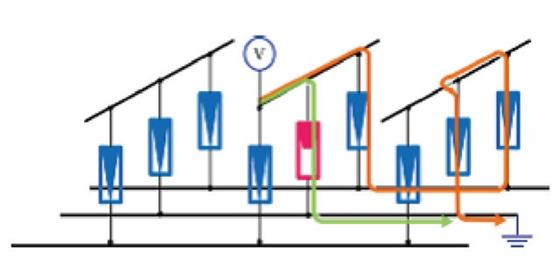

内存为提高集成电路上的密度,发展出一种排列结构方式,称为交叉数组(Crossbar Array)[24-26],这种方式虽拥有较高的组成密度,但采用交叉数组结构会产生一个很大的问题,即潜行电流(Sneak Path Current)的产生(如图 12 所示),造成在读取特定组件状态时,受邻近组件影响导致状态误判。

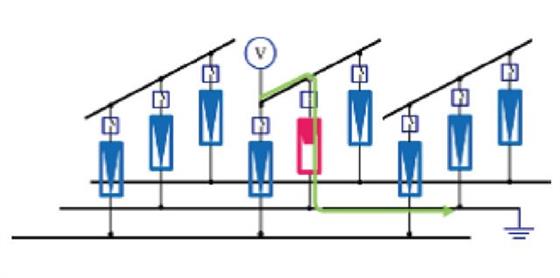

为了解决潜行电流的问题,现今 RRAM 组件已发展出多种架构以解决潜行电流的问题(图13),包括将 RRAM 与晶体管(Transistor)组成的 1T1R 架构 [26-27],或是 RRAM 与选择器(Selector)组成的 1S1R [28-29] 架构等方式。其中 1T1R 架构因结构简单且兼容于现今 CMOS 制程受到广泛重视,目前多用于强调操作速度与低成本的嵌入式内存(Embedded Memory)上,并与微控制器(Microcontroller Unit)相互结合,进一步提升其效能。

▲图 12 RRAM 形成数组因潜行电流造成组件读取误判

▲图 13 RRAM 搭配一开关可解决潜行电流问题

然而在晶体管尺寸持续微缩的状况下,其能承受的电压将越来越小,这将使 RRAM 可能面临到操作电压不足的问题,为解决此问题势必需从结构与材料着手。而除了制程上的发展外,由于 RRAM 于 1T1R 架构组件特性,近年来也衍生出相关仿生与逻辑运算等重要的新颖应用 [30-32]。

RRAM 组件近年衍生的新颖应用

由于人工智能(Artificial Intelligence, AI)的快速发展,其相关应用包括影像辨识、语音识别、智能监控、智慧驾驶等均受到广泛瞩目,而深度学习等技术亦具备庞大发展潜能。在 AI 相关技术中,最被广为应用的即是机器学习,机器学习乃是利用多层次人工神经网络(Artificial Neural Networks, ANN)进行数据学习,RRAM 组件因具备非挥发性(Non-Volatility)与多位存储(Multi-Bit Storage)之特性,加上低耗能、高操作速度等优点,近年来产生许多新颖应用,包括类神经型态(Neuromorphic)与非范纽曼(Non-Von-Neumann)架构的智能运算。

因此基于先前研究成果,在薄膜晶体管结合 RRAM 组件所成为的 1T1R 架构下,透过组件数组运用于智能运算的主要架构,其中欲探讨并解决的问题有三项:

- 结合组件特性与制程,实现仿生 RRAM 数组结构。

- 利用 RRAM 组件数组结构进一步实现逻辑运算。

- 最终于 RRAM 组件数组实现人工神经网络的智能运算。

何谓仿生技术?

仿效生物能力以提升科学技术称之为仿生(Bionic)。生物世界历经数十亿年不断演化,为了适应多变生态系环境,生物往往发展出十分精致且节能的功能,电子组件利用仿效大脑神经的仿生技术,将为未来电子科技带来突破性发展。

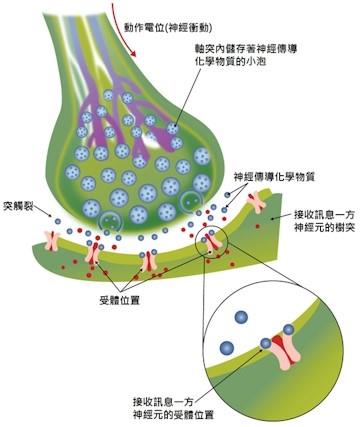

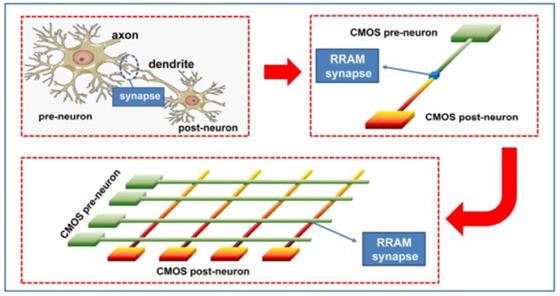

人类的大脑即是相当好的例子,大脑是一个高效率且低功耗的系统,不只能够传递讯息,且具有学习与记忆的能力。人脑神经元间的连结称为突触(ynapse)(图 14),突触间的传导行为在讯息传递的过程中扮演相当重要的角色。

突触间的连接强度具有可调性,称为脉冲时序依赖可塑性(Spike-timing-dependent plasticity, STDP),藉由调节进行增益(Potentiation)或抑制(Depression)[33],进行整合后再依体内电位变化,决定是否藉由突触输出神经传导物质至下个神经元中,STDP 同时也是神经生物学中被认为是构成记忆和学习的重要基础。

▲图 14 人脑神经元及突触示意图

未来利用电子组件仿效大脑神经讯息传递与学习记忆方式,将使电子科技与应用产生突破性发展。现代计算机储存记忆系以 0 和 1 的数字讯号来进行运算与记忆,而人脑不同于计算机是以模拟讯号来进行传递讯息与储存记忆,藉由对人类中枢神经系统的观察进而启发 ANN 概念。

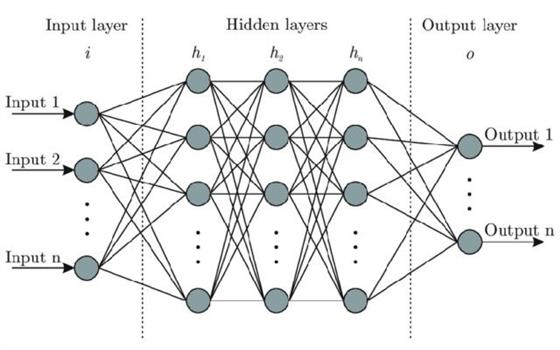

如同大脑中神经元(Neurons)构成人类的神经网络,ANN 是由许多节点运算单元(Nodes)互相链接(图 15),通常可区分成三个部分,即输入层、隐藏层(通常可为多层)与输出层。每一层的所有节点皆与前、后层的节点连结 [34],彼此连接形成类神经网络结构,藉数学计算模型对函式进行估算近似而得输出结果,使 ANN 在人脑所擅长如图像语音识别、分类、预测、记忆等领域具备高度发展潜力。

▲图 15 人工神经网络架构示意图 [34]

RRAM 组件于仿生技术的应用

要了解 RRAM 组件如何于此领域的应用,则需了解 RRAM 组件的多重组态特性(Multi-level Resistance Characteristics),其相关研究与控制方法近年已受到广泛重视 [35-37],对于单颗组件的多重阻态操作方式为:当组件在 Set 过程时,设定不同的限制电流使组件 LRS 阻值可分为多重阻态;而 Reset 过程则利用不同截止电压范围,使得 HRS 可得不同阶层变化的阻值,如此即可在单一内存组件上拥有多位存取的能力。

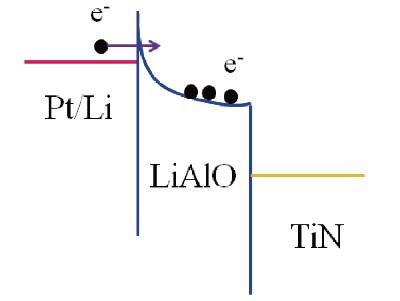

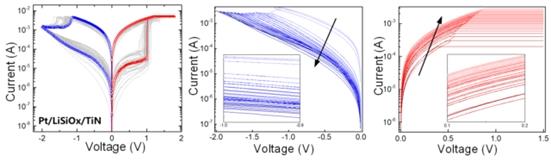

图 16 为一 Pt/LiSiOx/TiN 组件,具有良好多位储存功能,我们操作在不同的 Reset 截止电压与 Set 限制电流条件下,可以使组件阻值变化状态成为连续态形式,此电阻变化形式又称为模拟式(Analog)电阻转换特性。

▲图 16 Pt/LiSiOx/TiN 组件直流特性、Reset 与 Set 过程之渐进变化情形

由于上述的操作方式在电路设计与运用上相当复杂,故将 RRAM 组件产生类式的连续态形式尚有另一种操作方法,即利用固定截止电压对组件进行连续扫描(Consecutive Voltage Sweeping),藉由电压扫描方式渐进式地操作改变组件电阻状态。

如图 17 所示,当 Pt/LiSiOx/TiN 组件以 DC 操作时,若输入一个小于 Reset 电压并连续操作状态下,其电流会缓慢下降而阻态会渐渐上升;反之,若输入一个小于 Set 电压并连续操作,其电流会缓慢上升阻态会渐渐下降。若将操作电压与电流对时间轴作图,即可发现组件的阻值状态亦呈现渐进方式转换。上述除利用电阻值或电流参数呈现组件切换特性外,一般研究则多以电导(Conductance)变化呈现组件阻值变换特性。

▲图 17 Pt/LiSiOx/TiN 组件已连续定电压扫描下,阻值呈渐进方式变

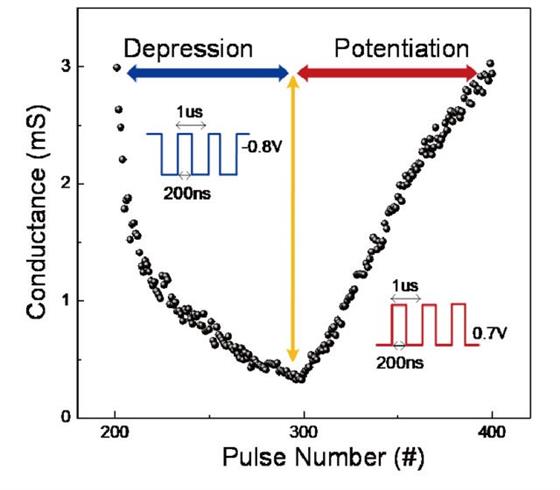

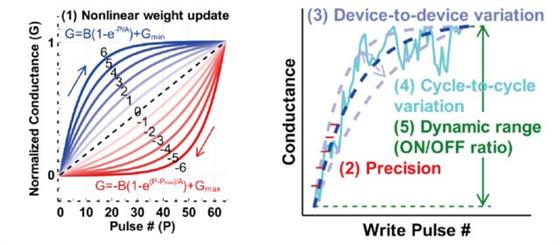

RRAM 组件如欲仿效突触的行为,则需利用组件电导(电阻)的渐变特性模拟突触权重的连续调节,进而模拟突触的可塑性,因此相关 RRAM 组件的突触特性关键参数相当重要,包括:

- Linearity:电导调节线性度

- Precision:权重(电导值)调节精度

- ON/OFF Ratio:在脉冲操作下组件可调节的最大与最小电导值范围

- Variation:组件的 Cycle-to-Cycle & Device-to-Device 变化度

- Defective Rate:组件数组良率(Yield)与阻态保持(Retention)特性

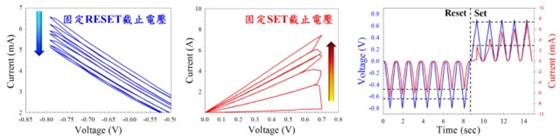

图 18 系将 Pt/LiSiOx/TiN 组件利用连续脉波操作,以验证组件仿真神经元突触的仿生特性,藉由调整脉波电压大小、脉冲时间、脉波次数,即可改变组件阻态与导电性,使组件组态由 LRS 连续缓升至 HRS,再从 HRS 缓降至 LRS,以连续正负电压脉波操作仿真电阻增益(Potentiation)及抑制(Depression)行为。

▲图 18 Pt/LiSiOx/TiN组件以连续脉波操作下阻值逐渐变化与 STDP 测试结果

由 STDP 实验结果显示,此组件仿效大脑突触行为将有助于类神经网络的发展。RRAM 欲作为仿生组件使用,则其阻值变化状态须具备连续态形式,藉以反复设定多种突触权重数值应用于类神经运算。理想的 RRAM 组件运用于突触操作的需求包括 [38](图19、图20):

- 稳定多阶的电导状态数

- 在脉冲操作下,拥有线性且对称的组件电导值变化

- 良好的组件均匀度,减小 Cycle-to-Cycle、Device-to-Device 的变化

- 足够的组件电导变化范围(ON/OFF Ratio)

▲图 19 RRAM 组件有效电导状态

▲图 20 RRAM 组件的突触特性关键参数 [38]

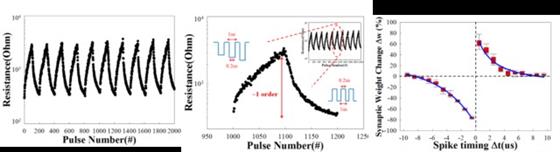

通常接口型 RRAM 组件的阻态变化虽较为线性,但是因其记忆窗口、持久性(Retention)与耐读写度(Endurance)的可靠度较差,实际运用上有相当难度,故寻求阻值变化具高度线性的 RRAM 组件对于仿生组件操作相当重要。

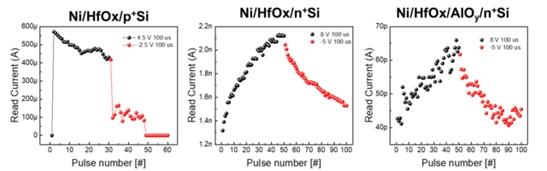

先前研究结果显示,RRAM 组件中间绝缘层若含有高氧空缺密度,容易形成导电路径,其电阻转换多为突升或突降,意谓着电阻切换行为如同数字讯号的 0 与 1,无法表现出模拟式的电阻渐变切换行为;而绝缘层中含氧空缺密度的 RRAM 组件,可能较有机会表现出模拟式电阻切换特性,同时能兼具较佳的可靠度 [38-39]。除了 LiSiOx 材料外,先前实验结果亦发现基于 HfOx 材料结合不同电极或迭层组合,也可具备模拟式电阻转换特性(图21)。

上述 RRAM 组件仿生特性均基于单一组件,未来如何结合相关材料特性与组件制程,开发兼具模拟式电阻切换特性及高可靠度的 RRAM 数组仿生电子组件(图 22),值得相关研究人员后续深入探讨并解决相关问题。

▲图 21 HfOx 材料结合不同电极或迭层组合实现模拟式电阻切换特性

▲图 22 模拟式 RRAM 组件由单一组件进而形成数组组件,对于仿生电子组件发展有相当重要性 [35]

应用潜力巨大,仍不是最终答案?

本篇针对电阻式内存的技术架构及其应用提供了全面性介绍,同时也清楚阐述了该组件运作时电阻非线性变化的物理机制,以利读者快速了解此最具市场潜力的前瞻技术。

尽管电阻式内存应用潜力巨大,至今大多数仍然处于开发阶段,目前为止有对外供货的公司仅 Crossbar、Panasonic 与 Adesto 三家而已。然而,为何业界普遍认为,电阻式内存将在未来 3 至 4 年内迎来快速成长?其为何又被视为第四种被动组件?而电阻式内存在逻辑运算与智能运算上又有哪些发展?将在下篇探讨。

参考数据:

[1] Hickmott, T. W. “Low‐frequency negative resistance in thin anodic oxide films." Journal of Applied Physics 33.9 (1962): 2669-2682.

[2] Yun, Jung‐Bin, et al. “Random and localized resistive switching observation in Pt/NiO/Pt." physica status solidi (RRL)–Rapid Research Letters 1.6 (2007): 280-282.

[3] Akoh, N., et al. “A ReRAM-based analog synaptic device having spike-timing-dependent plasticity." IEICE Tech Rep 110.246 (2010): 23-28.

[4] Hu, S. G., et al. “Emulating the paired-pulse facilitation of a biological synapse with a NiOx-based memristor." Applied Physics Letters 102.18 (2013): 183510.

[5] Hu, S. G., et al. “Synaptic long-term potentiation realized in Pavlov’s dog model based on a NiOx-based memristor." Journal of Applied Physics 116.21 (2014): 214502.

[6] Ho, Patrick WC, et al. “Comparison between Pt/TiO2/Pt and Pt/TaOx/TaOy/Pt based bipolar resistive switching devices." Journal of Semiconductors 37.6 (2016): 064001.

[7] Bousoulas, P., et al. “Engineering amorphous-crystalline interfaces in TiO2−x/TiO2−y-based bilayer structures for enhanced resistive switching and synaptic properties." Journal of Applied Physics 120.15 (2016): 154501.

[8] Mostafa, Hesham, et al. “Implementation of a spike-based perceptron learning rule using TiO2−x memristors." Frontiers in neuroscience 9 (2015): 357.

[9] Park, Jaesung, et al. “TiOx-based RRAM synapse with 64-levels of conductance and symmetric conductance change by adopting a hybrid pulse scheme for neuromorphic computing." IEEE Electron Device Letters 37.12 (2016): 1559-1562.

[10] Kim, Seonghyun, et al. “Defect engineering: reduction effect of hydrogen atom impurities in HfO2-based resistive-switching memory devices." Nanotechnology 23.32 (2012): 325702.

[11] Nardi, Federico, et al. “Complementary switching in oxide-based bipolar resistive-switching random memory." IEEE transactions on electron devices 60.1 (2012): 70-77.

[12] Padovani, Andrea, et al. “Microscopic modeling of HfOx RRAM operations: From forming to switching." IEEE Transactions on electron devices 62.6 (2015): 1998-2006.

[13] Shang, Jie, et al. “Highly flexible resistive switching memory based on amorphous-nanocrystalline hafnium oxide films." Nanoscale 9.21 (2017): 7037-7046.

[14] Sawa, Akihito. “Resistive switching in transition metal oxides." Materials today 11.6 (2008): 28-36.

[15] Chang, Ting-Chang, et al. “Resistance random access memory." Materials Today 19.5 (2016): 254-264.

[16] Waser, Rainer, et al. “Redox‐based resistive switching memories–nanoionic mechanisms, prospects, and challenges." Advanced materials 21.25-26 (2009): 2632-2663.

[17] Rainer Waser, et al. “Nanoionics-based resistive switching memories." Nature Materials 6 (2007): 833-840.

[18] Y.-S. Lai, et al. “Charge-transport characteristics in bistable resistive poly (N-vinylcarbazole) films." IEEE Electron Device Letters 27 (2006): 451-453.

[19] K.-C. Chang, et al. “Reducing operation current of Ni-doped silicon oxide resistance random access memory by supercritical CO2 fluid treatment." Applied Physics Letters 99 (2011): 263501-1-4.

[20] S. Yu, et al. “Conduction mechanism of TiN/HfOx/Pt resistive switching memory: A trap-assisted-tunneling model." Applied Physics Letters 99 (2011): 063507-1-3.

[21] C. Kuan-Chang, et al. “Hopping effect of hydrogen-doped silicon oxide insert RRAM by supercritical CO2 fluid treatment." IEEE Electron Device Letters 34 (2013): 617-619.

[22] S. M. Sze, et al. “Physics of semiconductor devices." John Wiley & Sons, New York (2006): 227-228.

[23] Y.-E. Syu, et al. “Asymmetric Carrier Conduction Mechanism by Tip Electric Field in Resistance Switching Device." IEEE Electron Device Letters 33 (2012): 342-344.

[24] Luo, Qing, et al. “Super non-linear RRAM with ultra-low power for 3D vertical nano-crossbar arrays." Nanoscale 8.34 (2016): 15629-15636.

[25] Tsai, Cheng-Lin, et al. “Resistive random access memory enabled by carbon nanotube crossbar electrodes." Acs Nano 7.6 (2013): 5360-5366.

[26] Lee, Daeseok, et al. “Oxide based nanoscale analog synapse device for neural signal recognition system." Electron Devices Meeting (IEDM), 2015 IEEE International. IEEE, 2015.

[27] Niu, Gang, et al. “Material insights of HfO2-based integrated 1-transistor-1-resistor resistive random access memory devices processed by batch atomic layer deposition." Scientific reports 6 (2016): 28155.

[28] Chen, Pai-Yu, and Shimeng Yu. “Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design." IEEE Transactions on Electron Devices 62.12 (2015): 4022-4028.

[29] Kim, Sungho, Jiantao Zhou, and Wei D. Lu. “Crossbar RRAM arrays: Selector device requirements during write operation." IEEE Transactions on Electron Devices 61.8 (2014): 2820-2826.

[30] Tosson, Amr MS, et al. “A study of the effect of RRAM reliability soft errors on the performance of RRAM-based neuromorphic systems." IEEE Transactions on Very Large Scale Integration (VLSI) Systems 25.11 (2017): 3125-3137.

[31] Zangeneh, Mahmoud, and Ajay Joshi. “Design and optimization of nonvolatile multibit 1T1R resistive RAM." IEEE Transactions on Very Large Scale Integration (VLSI) Systems 22.8 (2013): 1815-1828.

[32] Wang, Zhuo-Rui, et al. “Functionally complete Boolean logic in 1T1R resistive random access memory." IEEE Electron Device Letters 38.2 (2016): 179-182.

[33] Bi, Guo-qiang, and Mu-ming Poo. “Synaptic modifications in cultured hippocampal neurons: dependence on spike timing, synaptic strength, and postsynaptic cell type." Journal of neuroscience 18.24 (1998): 10464-10472.

[34] https://www.tutorialspoint.com/artificial_intelligence/artificial_intelligence_neural_networks.htm

[35] Park, Sangsu, et al. “Nanoscale RRAM-based synaptic electronics: toward a neuromorphic computing device." Nanotechnology 24.38 (2013): 384009

文章来源:TechNews